### Quick Start Guide MagniV<sup>®</sup> MC9S12ZVML128 MCU

Three-phase Sensorless PMSM Motor Control Development Kit

#### **Quick Start Guide**

### THREE-PHASE SENSORLESS PMSM KIT WITH MagniV MC9S12ZVML128 MCU

#### THREE-PHASE SENSORLESS PMSM KIT WITH MagniV MC9S12ZVML128 MCU

#### Hardware

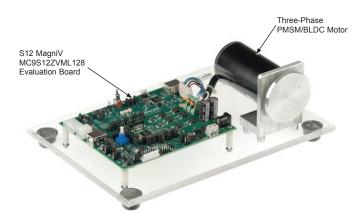

- MagniV MC9S12ZVML128 evaluation board with integrated 3-phase 12 V/10 A power stage

- Three-phase PMSM/BLDC motor with HALL sensor, 24 VDC, 9350 RPM, 90 W, 45ZWN2490B

- USB cable

- 12 VDC power supply

#### Resources

- Sensorless field-oriented control of PMSM using Back-EMF observer

- Automotive math and motor control library set for MC9S12ZVM installation package

- FreeMASTER installation package

- FreeMASTER project including Motor Control Application Tuning tool

- Three-Phase Sensorless PMSM Kit with MagniV MC9S12ZVML128 MCU Fact Sheet

- Three-phase Sensorless PMSM Kit with MagniV MC9S12ZVML128 MCU Quick Start Guide

- 3-Phase Sensorless PMSM Kit with MagniV MC9S12ZVML128 MCU Application Note

- MagniV MC9S12ZVML128 Evaluation Board User Guide

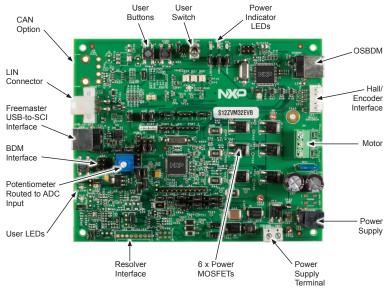

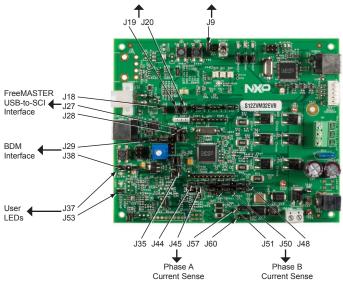

#### GET TO KNOW THE MagniV MC9S12ZVML128 EVALUATION BOARD

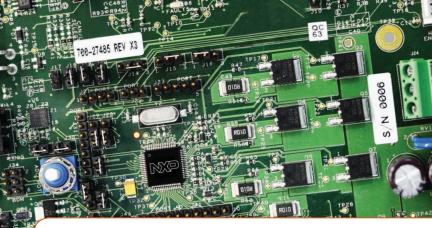

Front side of MagniV MC9S12ZVML128

### SOFTWARE TOOLS INSTALLATION

Install the FreeMASTER debugging tool. For FreeMASTER application download, please visit

#### www.nxp.com/freemaster.

Install the CP210x virtual COM port 2 Install the Cr 2102 Virtual COM driver. For the CP210x virtual COM port driver installation file, please visit Downloads section at www.nxp.com/automcdevkits.

Run "Device Manager" on your system. Check which COM port was assigned to the CP210x COM port driver.

Connect the USB cable to the MagniV MC9S12ZVML128 evaluation board and the host PC.

Connect the power supply to the MagniV MC9S12ZVML128 evaluation board

Start the FreeMASTER project MC9S12ZVML128\_PMSM\_Sensorles s.pmp located in MTRCKTSPN7VM128\SW\ MC9S12ZVML128 PMSM Sensorless project directory.

Enable communication by pressing the "STOP" button in the FreeMASTER, or by pressing "CTRI +K "

Successful communication is signalized in the status bar. If the communication is not established, check the USB connection between the PC and MagniV MC9S12ZVML128 evaluation board, communication port and speed. The communication port and speed can be set in the Project\Options menu (or pressing "CTRL+T"). The communication speed must be set at 19200 Bd.

#### **Quick Start Guide**

### APPLICATION CONTROL

1 When the power supply is connected to the evaluation board the PMSM motor is in stop mode. To start the motor use the user switch. Blue LED1 (D14) connected to port PS4) of the MC9S12ZVML128 evaluation board has the following functionality:

- OFF if the application is in the READY, INIT states

- Slow flashing if the application is in the

- CALIB state (flashing with a period of 2 Hz)

- ALIGN state (flashing with a period of 4 Hz)

- ON if the application is in the RUN state

- · Fast flashing if the application is in the

- FAULT state (flashing with a period of 8 Hz)

2 If no actual faults are present in the system, all the LED-like indicators on the FreeMASTER MCAT Control Page will be dark red. If there is a fault present, identify the source of the fault and remove it. Successful removal is signalized by the switching off of the respective LED-like indicator on the FreeMASTER MCAT Control Page.

**3** Press the UP and DOWN (SW1 + SW2) buttons on the MC9S12ZVML128 evaluation board simultaneously to clear the fault status register once in the FAULT state. The application can be restarted by positioning the ON/OFF switch (SW3) on the MC9S12ZVML128 evaluation board to the RUN position (transition from STOP to RUN in case the switch was in the RUN state when the fault event occurred).

### **APPLICATION CONTROL (CONT.)**

4 If all the LED-like indicators on the FreeMASTER MCAT Control Page are off, clear pending faults by pressing the fault button "FAULT CLEAR" on the FreeMASTER MCAT Control Page, or alternatively by pressing the UP+DOWN buttons (SW2+SW1) on the MC9S12ZVML128 Evaluation Board simultaneously. The ON/OFF switch (SW3) on the MC9S12ZVML128 Evaluation Board must be in OFF position.

5 Start the application by pressing "RUN" on the (ON/OFF) button on the FreeMASTER MCAT Control Page or by positioning the ON/OFF switch (SW3) on the MC9S12ZVML128 evaluation board to the ON position (transition from OFF to ON in case the switch was in the ON state when a fault event occurred). 6 Enter the required speed by assigning this value to the "Speed Required" variable in the variables watch window or by clicking on the speed gauge on the FreeMASTER MCAT Control Page. The value is in revolutions per minute. Alternatively, the rotor speed can be increased/decreased by pressing the UP/DOWN switches on the MC9S12ZVML128 evaluation board.

Stop the application by pressing "STOP" on the (ON/OFF) switch on the FreeMASTER MCAT Control Page, or by positioning the ON/OFF switch (SW3) on the MC9S12ZVML128 Evaluation Board to the OFF position.

| JUMPER | OPTION                                    | SETTING | DESCRIPTION                                                               |

|--------|-------------------------------------------|---------|---------------------------------------------------------------------------|

| J2     | CAN transceiver<br>5 V supply             | OPEN    | $\rm V_{_{DDC}}$ ballast transistor is not supplied from $\rm V_{_{SUP}}$ |

|        | option                                    | *CLOSE* | $V_{_{DDC}}$ ballast transistor is supplied from $V_{_{\rm SUP}}$         |

| J3     | V <sub>DDC</sub> supplied from USB option | *OPEN*  | $V_{\mbox{\tiny DDC}}$ node is not supplied from the USB-to-SCI interface |

|        |                                           | CLOSE   | $V_{\mbox{\tiny DDC}}$ node is supplied from the USB-to-SCI interface     |

| J4     | RESET LED<br>indicator option             | OPEN    | RESET LED indicator disabled                                              |

|        |                                           | *CLOSE* | RESET LED indicator enabled                                               |

| J5     | V <sub>DDX</sub> LED<br>indicator option  | OPEN    | $V_{_{DD}}$ LED indicator disabled                                        |

|        |                                           | *CLOSE* | $V_{_{DD}}$ LED indicator enabled                                         |

| J6     | OSJTAG<br>bootloader                      | OPEN    | V <sub>SUP</sub> LED indicator disabled                                   |

|        | selection                                 | *CLOSE* | V <sub>SUP</sub> LED indicator enabled                                    |

| JUMPER | OPTION                                           | SETTING | DESCRIPTION                                                       |

|--------|--------------------------------------------------|---------|-------------------------------------------------------------------|

| J9     | ON/OFF<br>switch option                          | OPEN    | ON/OFF switch disabled                                            |

|        |                                                  | *CLOSE* | ON/OFF switch enabled                                             |

| J10    | OSDBM<br>bootloader                              | *OPEN*  | OSBDM boot-loader disabled                                        |

|        | option                                           | CLOSE   | OSBDM boot-loader enabled                                         |

| J12    | Resolver circuit<br>5 V supply<br>option         | OPEN    | Resolver Inputs circuitry (+5VDC) supply disabled                 |

|        |                                                  | *CLOSE* | Resolver Inputs circuitry (+5VDC) supply enabled                  |

| J14    | EVDD or FAULT selector                           | 1–2     | FAULT input is connected to port PP0                              |

|        |                                                  | *2–3*   | Port PP0 is connected to EVDD at Hall sensor interface            |

| J15    | Resolver or Hall/<br>Encoder Phase<br>A selector | *1–2*   | Phase A from Resolver is connected to port PT1                    |

|        |                                                  | 2–3     | Phase A from Hall / Encoder interface is<br>connected to port PT1 |

| JUMPER | OPTION                                           | SETTING | DESCRIPTION                                                  |

|--------|--------------------------------------------------|---------|--------------------------------------------------------------|

| J16    | Resolver or Hall/<br>Encoder Phase<br>B Selector | *1–2*   | Phase B from Hall/Encoder interface is connected to port PT2 |

|        |                                                  | 2–3     | Phase B from Resolver is connected to port PT2               |

| J18    | USB-to-SCI<br>interface supply<br>option         | OPEN    | USB-to-SCI isolator supply disable                           |

|        |                                                  | *CLOSE* | USB-to-SCI isolator supply enabled                           |

| J19    | "UP" pushbutton option                           | OPEN    | "UP" push button disabled                                    |

|        |                                                  | *CLOSE* | "UP" push button enabled                                     |

| J20    | "DOWN"<br>pushbutton<br>option                   | OPEN    | "DOWN" push button disabled                                  |

|        |                                                  | *CLOSE* | "DOWN" push button enabled                                   |

| J27    | SCI RXD<br>selector                              | 1–2     | RXD from OSBDM is connected to port PS2                      |

|        |                                                  | *2–3*   | RXD from USB-to-SCI is connected to port PS2                 |

| JUMPER | OPTION                           | SETTING | DESCRIPTION                                           |

|--------|----------------------------------|---------|-------------------------------------------------------|

| J28    | SCI TXD<br>selector              | 1–2     | TXD from OSBDM is connected to port PS3               |

|        |                                  | *2–3*   | TXD from USB-to-SCI is connected to port PS3          |

| J29    | BDM interface<br>supply option   | OPEN    | BDM supply disabled                                   |

|        |                                  | *CLOSE* | BDM supply enabled                                    |

| J30    | ADC<br>potentiometer             | OPEN    | POT 1 (ADC potentiometer) supply disabled             |

|        | pull-up option                   | *CLOSE* | POT 1 (ADC potentiometer) supply enabled              |

| J33    | Microcontroller<br>supply option | OPEN    | MCU supply disabled                                   |

|        |                                  | *CLOSE* | MCU supply enabled                                    |

| J35    | ADC mapping-<br>PAD0             | *1–2*   | Connects PAD0 to AMP0 external gain-setting resistors |

|        |                                  | 2–3     | Connects PAD0 to POS_SIN resolver output              |

| JUMPER | OPTION                                       | SETTING | DESCRIPTION                                                                                                |

|--------|----------------------------------------------|---------|------------------------------------------------------------------------------------------------------------|

| J36    | V <sub>REF</sub> generation<br>supply option | OPEN    | Disconnects $V_{_{SUP}}$ to supply a regulated voltage at $V_{_{REF2}}$                                    |

|        |                                              | *CLOSE* | Connects $V_{_{\mbox{\scriptsize SUP}}}$ to supply a regulated voltage at $V_{_{\mbox{\scriptsize REF2}}}$ |

| J37    | USER LED1<br>option                          | OPEN    | "User LED1" disabled                                                                                       |

|        |                                              | *CLOSE* | "User LED1" enabled                                                                                        |

| J38    | PDO-PDOCLK                                   | *OPEN*  | PDO-PDOCLK not shorted                                                                                     |

|        |                                              | CLOSE   | PDO-PDOCLK shorted                                                                                         |

| J39    | Resolver<br>phase B<br>selector              | *1–2*   | Pins 1-2 closed—SINCOS I/O connector Phase B connected to Resolver Phase B input                           |

|        |                                              | 2–3     | Pins 2-3 closed—POS_COS connected to<br>Resolver Phase B input                                             |

| J40    | V <sub>DDX</sub> ballast<br>supply option    | OPEN    | V <sub>DDX</sub> ballast is disconnected                                                                   |

|        |                                              | *CLOSE* | $V_{_{DDX}}$ ballast is connected                                                                          |

| JUMPER | OPTION                   | SETTING | DESCRIPTION                                                            |

|--------|--------------------------|---------|------------------------------------------------------------------------|

| J43    | Resolver<br>circuit 12 V | OPEN    | Resolver generator circuit supply disconnected                         |

|        | supply option            | *CLOSE* | Resolver generator circuit supply connected                            |

| J44    | ADC mapping –<br>PAD1    | OPEN    | PAD1 is disconnected from the AMPM0 external<br>gain-setting resistors |

|        |                          | *CLOSE* | PAD1 is connected to the AMPM0 external gain-setting resistors         |

| J45    | ADC mapping –<br>PAD2    | OPEN    | PAD2 is disconnected from the AMPP0 external gain-setting resistors    |

|        |                          | *CLOSE* | PAD2 is connected to the AMPP0 external gain-<br>setting resistors     |

| J46    | ADC mapping –<br>PAD3    | *1–2*   | Connects PAD3 to ADC_IA (phase A current sense from external op-amp)   |

|        |                          | 2–3     | Connects PAD3 to POS_SIN resolver output                               |

| JUMPER | OPTION               | SETTING | DESCRIPTION                                                          |

|--------|----------------------|---------|----------------------------------------------------------------------|

| J47    | ADC mapping—<br>PAD4 | *1–2*   | Connects PAD4 to ADC_IB (phase B current sense from external op-amp) |

|        |                      | 2–3     | Connects PAD4 to ADC potentiometer POT1                              |

| J48    | ADC mapping—<br>PAD5 | *1–2*   | Connects PAD5 to AMP1 external gain setting resistors                |

|        |                      | 2–3     | Connects PAD5 to ADC_IB (phase B current sense from external op-amp) |

| J49    | Resolver<br>phase A  | *1–2*   | Resolver phase A connected to SINCOS I/O connector Phase A input     |

|        | selector             | 2–3     | Resolver phase A connected to Resolver POS_<br>SIN Schmitt-Trigger   |

| J50    | ADC mapping—<br>PAD6 | *1–2*   | Connects PAD6 to AMPM1 external<br>gain-setting resistors            |

|        |                      | 2–3     | Connects PAD6 to POS_COS resolver output                             |

| JUMPER | OPTION                    | SETTING              | DESCRIPTION                                                          |

|--------|---------------------------|----------------------|----------------------------------------------------------------------|

| J51/42 | ADC mapping—<br>PAD7      | *J51 (1–2)*          | Connects PAD7 to AMPP1 external gain-setting resistors               |

|        |                           | J51 (2–3)            | Connects PAD7 to POS_SIN resolver output                             |

|        |                           | J42 (1) –<br>J51 (2) | Connects PAD7 to ADC potentiometer POT1                              |

| J52    | ADC mapping—<br>PAD8      | *1–2*                | Connects PAD8 to ADC_IC (phase C current sense from external op-amp) |

|        |                           | 2–3                  | Connects PAD8 to POS_COS resolver output                             |

| J53    | USER LED2<br>option       | OPEN                 | "User LED 2" disabled                                                |

|        |                           | *CLOSE*              | "User LED 2" enabled                                                 |

| J55    | V <sub>REF</sub> selector | *1–2*                | $V_{\rm REF}$ supplied from $V_{\rm DDX}$                            |

|        |                           | 2–3                  | $V_{\rm REF}$ supplied from the $V_{\rm REF2}$ regulator             |

|        | 1                         | 1                    |                                                                      |

| JUMPER | OPTION                                             | SETTING | DESCRIPTION                                                                         |

|--------|----------------------------------------------------|---------|-------------------------------------------------------------------------------------|

| J56    | Resolver COS<br>reference                          | *1–2*   | Input to POS_COS circuit is from OFFSET1                                            |

|        |                                                    | 2–3     | Input to POS_COS circuit is from RES_COS_REF                                        |

| J57    | Internal AMP0<br>input selector<br>(inverting)     | *1–2*   | Connects DC Bus to the internal AMP0 inverting input (Phase A current sense)        |

|        |                                                    | 2–3     | Connects Ground to the internal AMP0 inverting input (DC Bus current sense)         |

| J59    | Resolver SIN reference                             | *1–2*   | Input to POS_SIN circuit is from RES_SIN_REF                                        |

|        |                                                    | 2–3     | Input to POS_SIN circuit is from OFFSET1                                            |

| J60    | Internal AMP0<br>input selector<br>(non-inverting) | *1–2*   | Connects Phase A to the internal AMP0<br>noninverting input (Phase A Current sense) |

|        |                                                    | 2–3     | Connects DC Bus as non-inverting input for internal AMP0 (DC Bus current sense)     |

| JUMPER | OPTION                   | SETTING | DESCRIPTION                       |

|--------|--------------------------|---------|-----------------------------------|

| J63    | FAULT<br>comparators 5 V | OPEN    | FAULT circuit supply disconnected |

|        | supply option            | *CLOSE* | FAULT circuit supply connected    |

Front side of MagniV MC9S12ZVML128

www.nxp.com

#### SUPPORT

Visit **www.nxp.com/support** for a list of phone numbers within your region.

#### WARRANTY

Visit **www.nxp.com/warranty** for complete warranty information.

Get Started Download installation software and documentation under "Jump Start Your Design" at www.nxp.com/automcdevkits.

#### www.nxp.com/automcdevkits

NXP, the NXP logo and MagniV are trademarks of NXP B.V. All other product or service names are the property of their respective owners. @ 2015–2016 NXP B.V.

Document Number: MTRCKTSPNZVM128QSG REV 1 Agile Number: 926-28715 REV B